AIT to Introduce Capillary Underfill to Provide Stress Relief with CTE of <16 ppm/°C for Stud Bumped Chip with 35μm Gap

Wafer level and chiplets packaging required capillary underfill having much lower CTE and capillary gap-filling than those used in BGA board level packaging. UF-MC7883-FP introduced by AIT has been proven to meet the reliability performance of low CTE and

Stress relief underfill for large area chip with copper pillar and gold bumps down to less than 35μm required different underfilling technology and solution

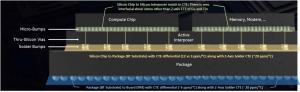

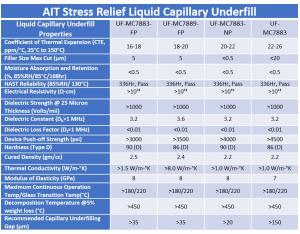

PRINCETON JUNCTION, NJ, UNITED STATES, July 11, 2023/EINPresswire.com/ -- With more semiconductor design and packaging utilizing fan-in and fan-out wafer level packaging (FO-WLP), underfill that can manage large area chip with copper pillar and gold bumps down to less than 35μm and advancing toward 25μm required different underfilling technology and solution.AI Technology, Inc. (AIT) have been utilizing its proprietary modified cyanate ester technology to provide both extra-high glass transition (Tg) and low viscosity for fast chip underfill successfully in the last few years. UF-MC7883-FP is a new generation of capillary underfill solution that have been proven to provide stress relief for chips with less than 35μm gap. With close to 80% fill with engineered micron sized silica, coefficient of thermal expansion (CTE) has been controlled to less 16 ppm/°C. The demonstrable low CTE and high Tg enable UF-MC7883-FP to provide slight compressive stress and low shear stress for WLP and package-on-package (PoP) and chiplets devices.

With AIT proprietary stress absorbing modified cyanate ester technology along with its controlled low CTE, even at high Tg of close to 220°C, the shear stress is controlled to minimal level to allow passing of the extreme thermal cycling requirements from -65°C to 150°C for the larger dies of 20mmx20mm. The inherent higher temperature stability of the cyanate ester molecular backbone, its has found some extreme applications at temperature beyond 175°C as well.

For more information on this new generation of low profile underfill for helping to achieve your 3-D chips and chiplets design and reliability, please visit us at booth 1546 of SEMICON WEST 2023.

Maurice Lebron

AI Technology, Inc.

+1 609-799-8896

ait@aitechnology.com

Legal Disclaimer:

EIN Presswire provides this news content "as is" without warranty of any kind. We do not accept any responsibility or liability for the accuracy, content, images, videos, licenses, completeness, legality, or reliability of the information contained in this article. If you have any complaints or copyright issues related to this article, kindly contact the author above.